要在6ULL执行C代码,则需要准备C语言执行环境,要执行的步骤为:

- 配置CPU,设置CPU的模式

- 配置SP指针

- 跳转到C代码

设置CPU的模式:

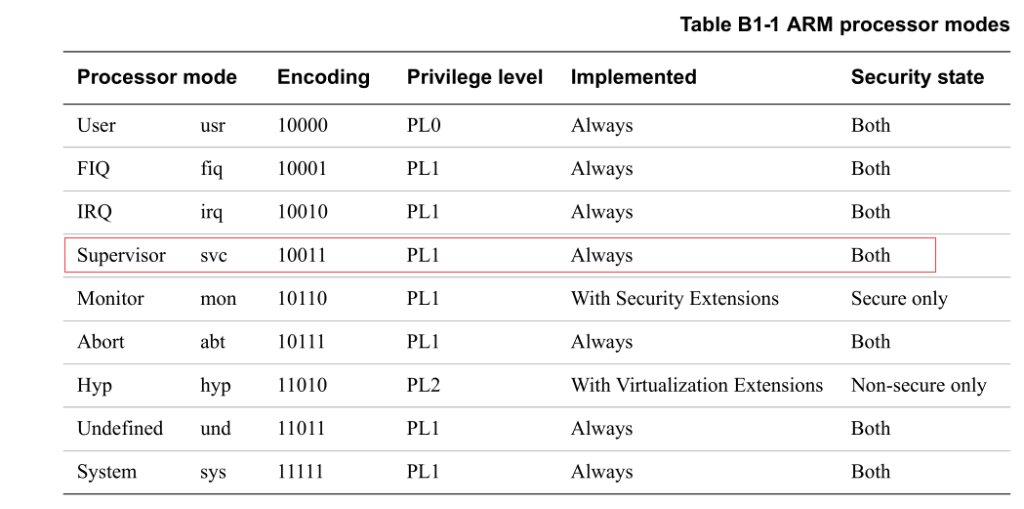

ARM Cortex-A7有9中运行模式:

在不同模式下,CPU的访问能力不同,要使CPU能够访问全部资源,则需要进入SVC模式。此时需要修改一个寄存器中的数据来达成此目的:The Current Program Status Register (CPSR)。

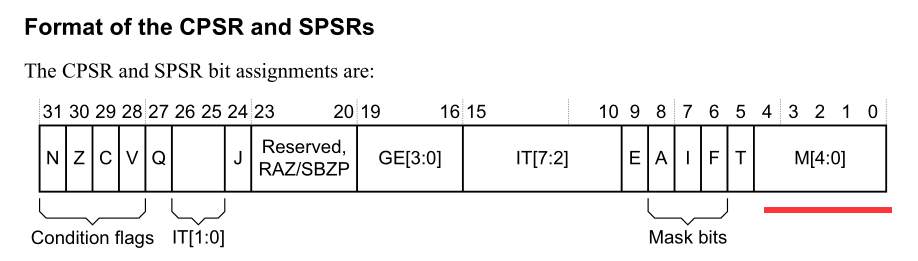

CPSR寄存器的功能如图所示:

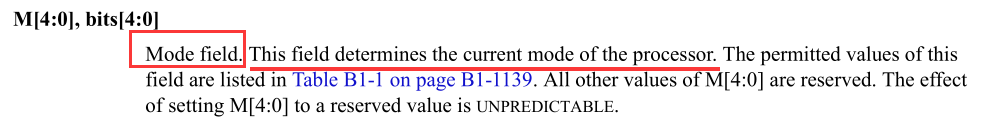

其中低5位M[4:0]决定了CPU当前的模式。

根据Table B1-1 ARM processor modes这张表可知,给CPSR寄存器写入5‘b10011即可进入SVC模式。那么可以使用LDR和STR来读写CPSR就可以了对吧?答案当然是不行!

因CPSR是状态寄存器(特殊寄存器),而LDR和STR用于通用寄存器的读写;要读写特殊寄存器,则需要MRS(从特殊寄存器读出到通用寄存器)指令和MSR(从通用寄存器写入到特殊寄存器)。

配置SP指针

SP可以指向内部RAM,也可以使用外部DDR。注意:CortexA7的栈生长方向是向下增长的(从高地址往低地址移动)。

若给栈分配的内存空间为0x80000000-0x80200000;则SP应指向0x80200000。

跳转到C代码

使用b指令,跳转到C语言的函数,比如main函数。

编写代码:

strat.s:

@start.s

.global __start

__start:

@进入SVC模式

MRS R0,CPSR @先读取CPSR寄存器当前值

@接下来要把保存在R0中的状态位[4:0]修改为10011

@要进行位操作,需要借助BIC指令和ORR指令,BIC进行位清除;ORR按位或

BIC R0,R0,#0x1F @低5位清零

ORR R0,R0,#0x13 @或运算

MSR CPSR,R0 @写入CPSR,进入SVC模式

@设置SP指针

LDR SP, =0x80200000 @向SP指针写入内存地址

@跳转到C语言的main函数

b mainmain.c:

Comments NOTHING